[FPGA/VerilogHDL/Xilinx]Vivado.Report之常规报告 |

您所在的位置:网站首页 › vivado drc rtstat-2 › [FPGA/VerilogHDL/Xilinx]Vivado.Report之常规报告 |

[FPGA/VerilogHDL/Xilinx]Vivado.Report之常规报告

|

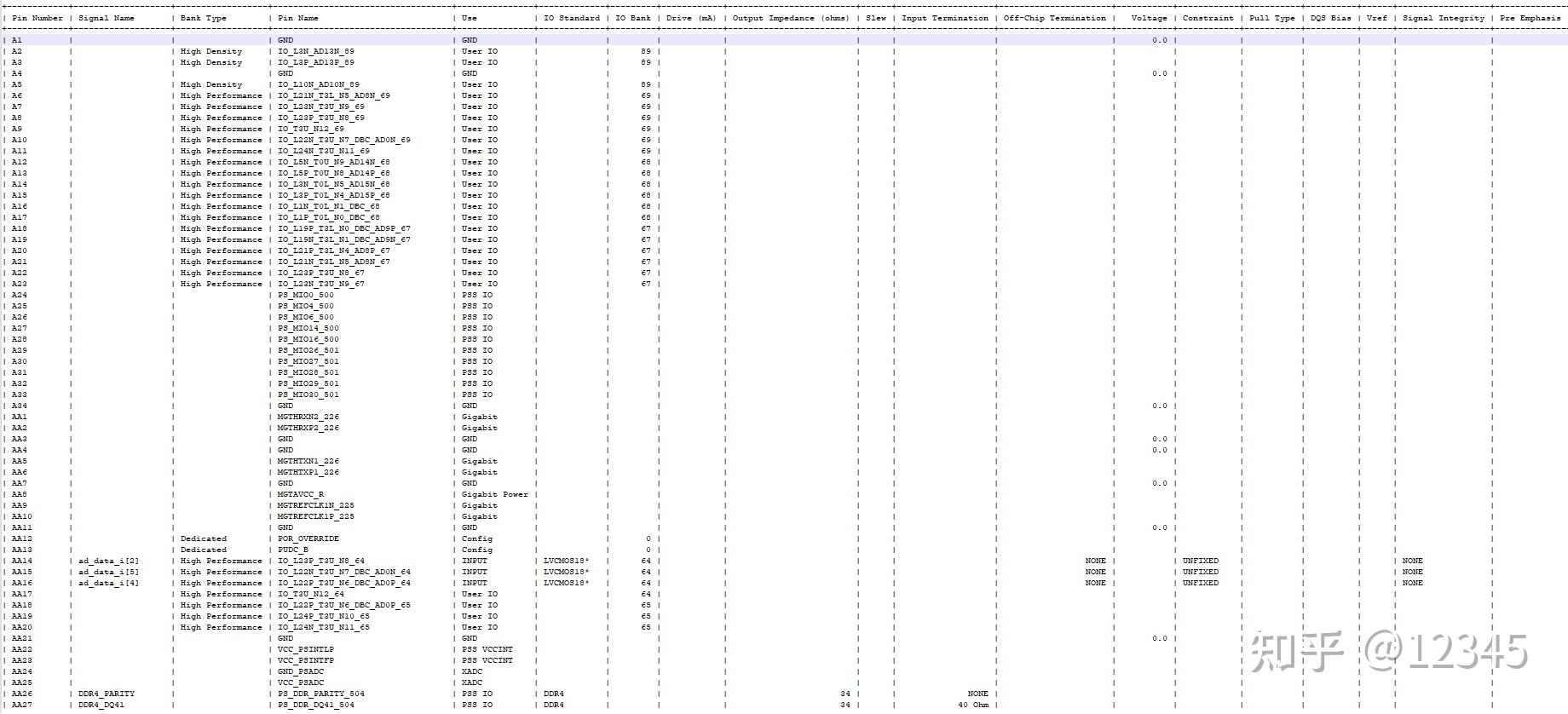

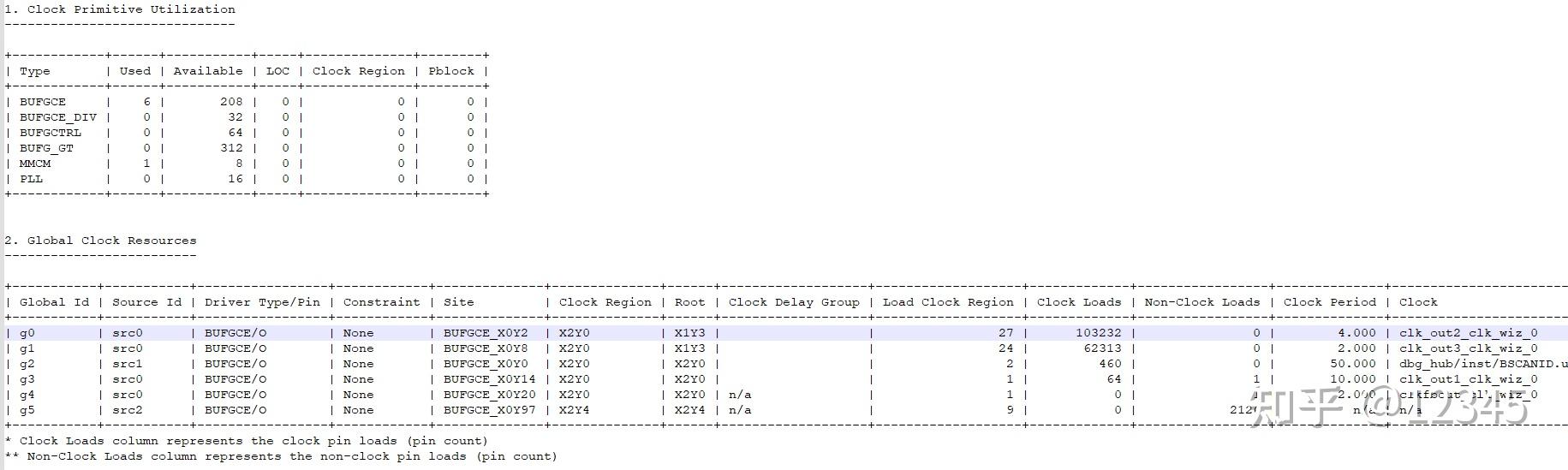

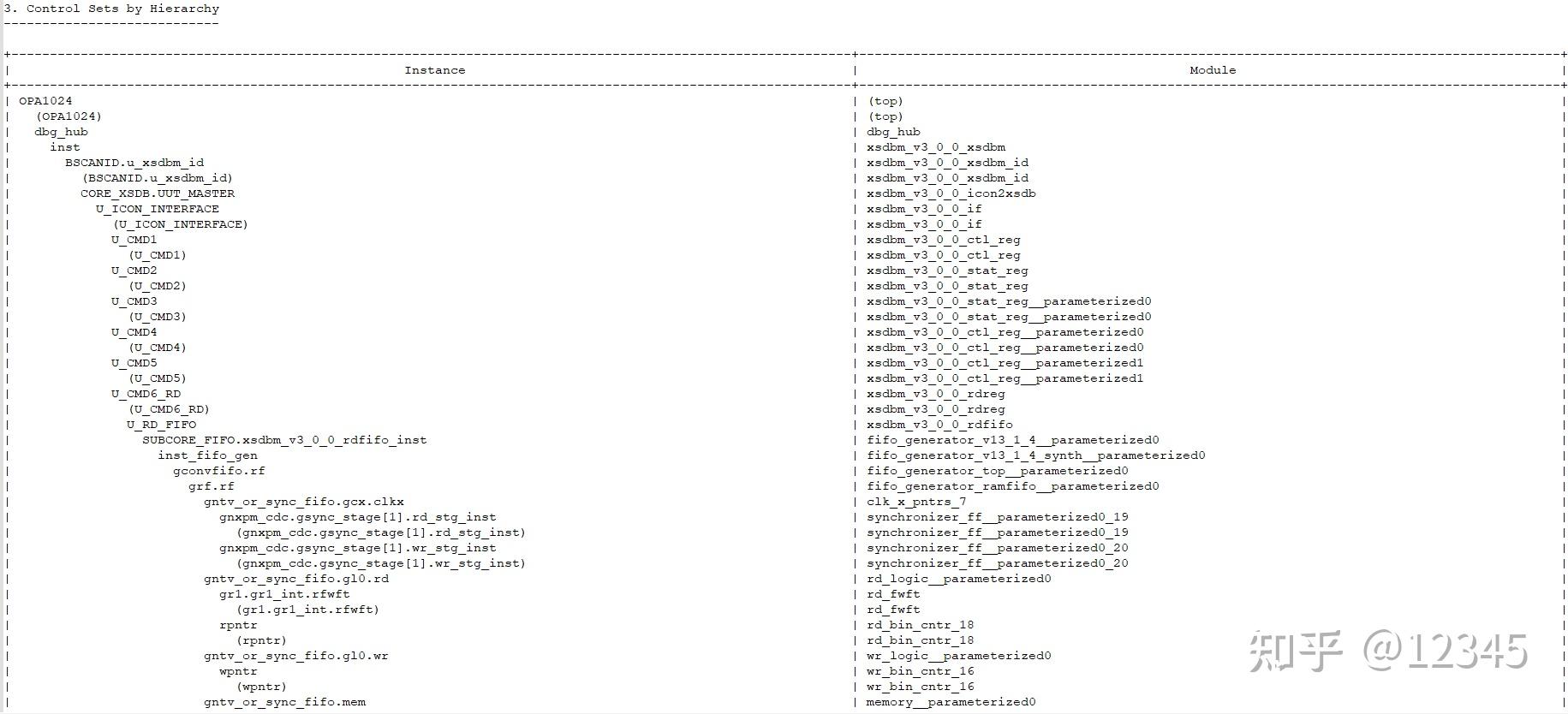

概述 在Vivado IDE中,主要有3种类型的报告,包括: 常规报告:涵盖了各种基于网表的报告以及功耗和 DRC。时序报告:涵盖了与时序约束相关的所有报告。设计收敛报告:涵盖了设计收敛阶段使用的报告。本文中,我们重点讲解常规报告的使用方法及相关功能。 常规报告Report Utilization“Report Utilization”(利用率报告)报告有助于从层级、用户定义的 Pblock 或 SLR 层面来分析含不同资源的设计的利用率。其中包含用于运行和使用以下对象的器件: CLB LogicSummary of Registers by TypeCLB Logic DistributionBLOCKRAMARITHMETICI/OCLOCKADVANCEDCONFIGURATIONPrimitivesBlack BoxesInstantiated Netlists当前工程的资源分布情况报告生成TCL脚本如下: report_utilization -file prj_util.rptIDE中将文件放入软件默认存放位置,并在tcl中进行提示: c:/Users/15010/AppData/Roaming/Xilinx/Vivado/prj_util.rpt简单放几个截图做示范,report的内容大致是这样:   Report I/O Report I/O“Report I/O”(引脚报告)可列出: SummaryIO Assignments by Package Pin当前工程的IO分布情况报告生成TCL脚本如下: report_io -file prj_io.rptIDE中将文件放入软件默认存放位置,并在tcl中进行提示: c:/Users/15010/AppData/Roaming/Xilinx/Vivado/prj_io.rpt简单放几个截图做示范,report的内容大致是这样:  Report Clock Utilization Report Clock Utilization“Clock Utilization”(时钟利用率)报告可帮助分析器件内时钟区域级别或时钟信号线级别的时钟原语和布线资源的利用率。它可用于调试时钟布局问题,并识别布局约束,从而最大限度提升资源利用率。“Clock Utilization”报告提供如下相关信息: Clock Primitive UtilizationGlobal Clock ResourcesGlobal Clock Source DetailsClock Regions : Clock PrimitivesClock Regions : Load PrimitivesClock Regions : Global Clock SummaryClock Regions : Routing Resource Utilization当前工程的时钟分布情况报告生成TCL脚本如下: report_clock_utilization -file prj_clk.rptIDE中将文件放入软件默认存放位置,并在tcl中进行提示: c:/Users/15010/AppData/Roaming/Xilinx/Vivado/prj_clk.rpt简单放几个截图做示范,report的内容大致是这样:  Report Power Report Power在布线后会生成“Power Report”(功耗报告),它基于当前器件工作条件和设计的切换率来报告功耗详情。功耗分析要求网表已完成综合或设计已完成布局布线。当“综合后设计”或“实现后设计”打开时,即可使用“Report Power”命令。 Report Control Sets控制集表示时钟信号、时钟使能信号和置位/复位信号的唯一组合。每个 slice 都支持有限数量的控制集,以供位于其中的触发器组合使用。根据所使用的架构,部分控制集允许在 slice 内共享。用户应熟悉目标系列的“Configurable Logic Block”(可配置逻辑块架构)才能理解兼容性规则。 报告主要包含以下 2 部分: 控制集的绝对数量。任意给定器件中控制集的有限数量。超出建议的控制集数量可能对 QoR 造成不利影响。控制器的负载剖析。需减少控制集时,减少包含少量负载的控制集数量最有效,因为这给设计增加的逻辑量最少。当前工程的控制集情况报告生成TCL脚本如下: report_control_sets -hierarchical -verbose -file prj_controlsets.rptIDE中将文件放入软件默认存放位置,并在tcl中进行提示: c:/Users/15010/AppData/Roaming/Xilinx/Vivado/prj_clk.rpt简单放几个截图做示范,report的内容大致是这样:   当然,controlsets的report有多种选择,可以参考我之前的文章. Report High Fanout Netsreport_high_fanout_nets 命令用于分析网表并报告具有最高扇出的信号线。此命令可在综合后、布局后或布线后网表上运行。但在布局前,此报告无法传递时钟区域和 SLR 信息。 当前工程的扇出情况报告生成TCL脚本如下: report_high_fanout_nets -file prj_fanouts.rpt简单放几个截图做示范,report的内容大致是这样:  当然,fanouts的report有多种选择,可以参考我之前的文章. |

【本文地址】